FPGAによるステッピングモータの台形加減速運転

2004/12/6 舞鶴高専 電子制御工学科 町田秀和

【2005/6/6】

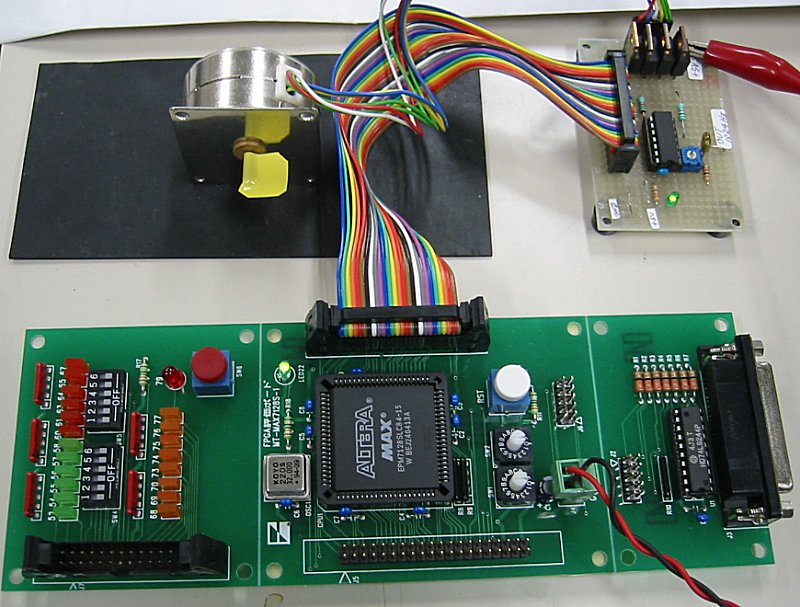

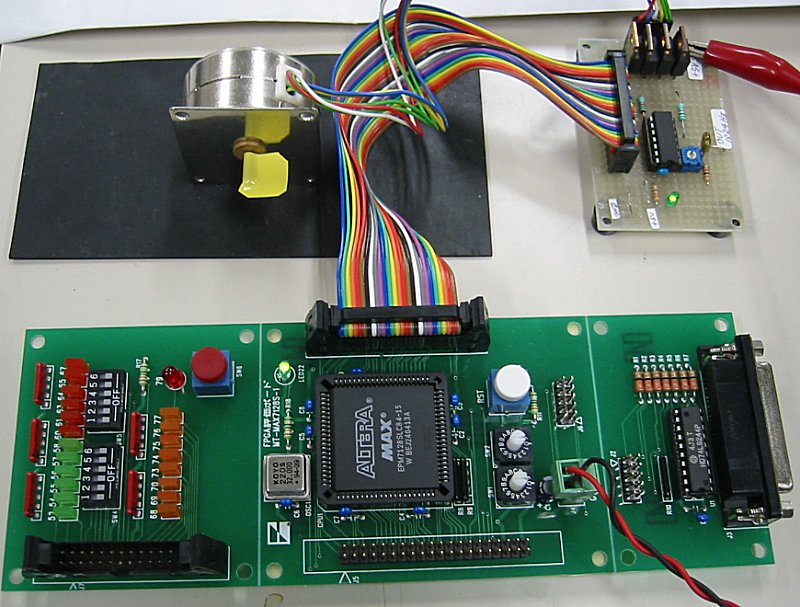

本システムを実現したFPGA(CPLD)評価基板(一番下までスクロールすると写真があります)を、

実費にて領布いたします。2004年度の公開講座用に使用したものの残部です。

本基板は、(1)FPGA部(EPM7128SLC84)、(2)I/O部、(3)バイトブラスタ部、の3つの部分より

構成されており、

Altera社のQuartusII Web Edition)(フリー(要登録))、電源(5V1A)、フラットケーブルを

用意するだけで、即座に使用することができます。

生基板と、全部品実装済の基板が少々残っています。ご入用の方はメールにてご連絡ください

(machida@maizuru-ct.ac.jp)

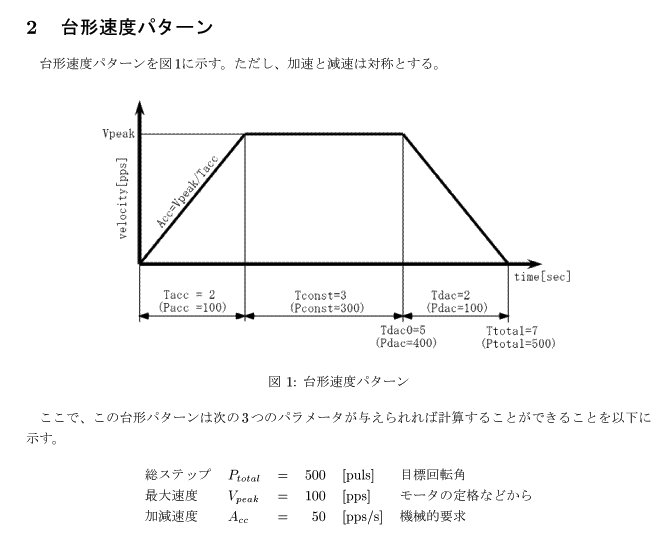

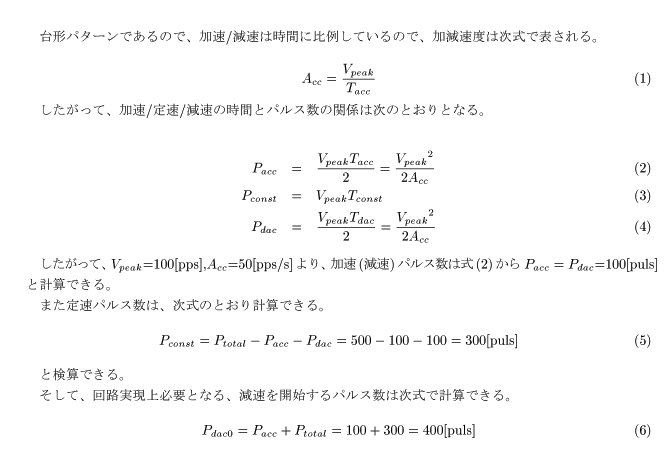

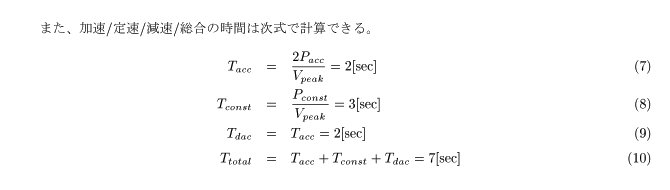

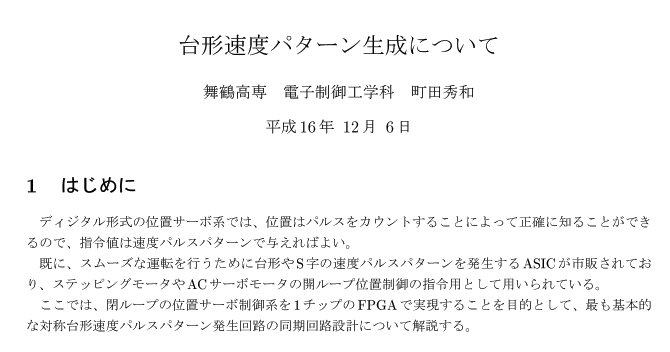

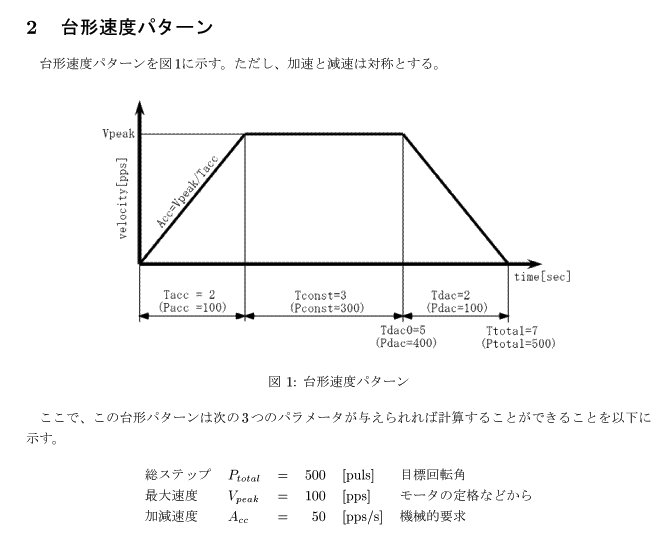

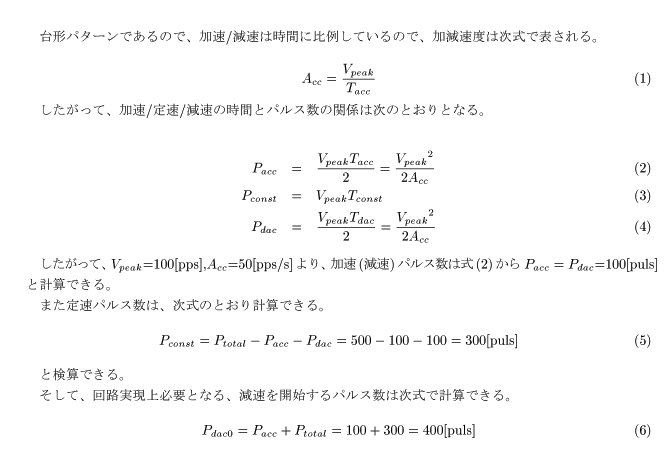

2004/12/13~の公開講座のネタとして設計した、

ステッピングモータの回転速度を、加速/定速/減速の台形の速度パターンで運転する

回路を紹介します。ステッピングモータの回転速度なら(PIC)マイコンのソフトウェアでも

十二分に実現可能ですが、ハードウェアにすればどうなるか分かると思います。

それでも、工夫すればACサーボモータの高速高精度駆動や複数モータの同期運転などに

使えると思います。

なお、このような「軌跡生成ASIC」は既に数社から市販されています。

(例:NOVA電子:大変高機能です)

下の写真をクリックして動画を再生し、加減速の様子をご覧下さい。

、

、

QuartusIIのソースファイル(LZH形式:450kbytes)←右クリックして保存してください。

、

、