- PLL,FPGAについて、ゼミや開発を行い理解を深められた。

- PLLモータ制御器は、DVDドライブなどの駆動に幅広く用いられている。 その特徴は、「PLL(位相同期制御系)」であるので完全に周波数および位相が、 基準となる水晶発振器入力に一致することである(クオーツ・ロック)

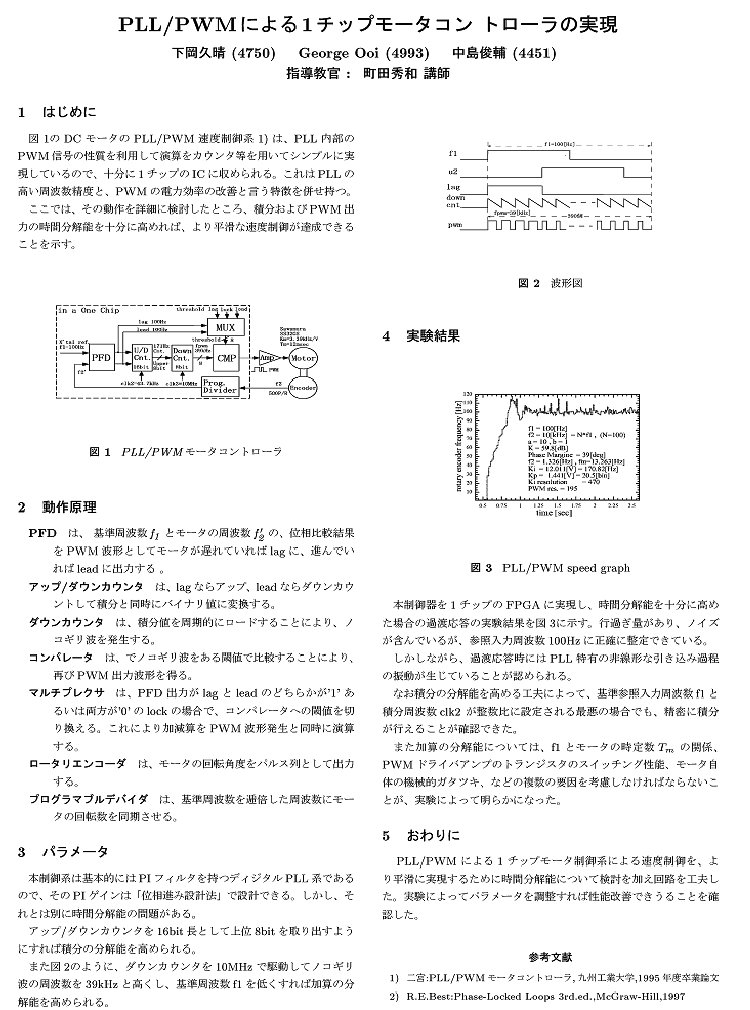

- 町田研究室で初めてFPGAを採用した。 FPGA評価ボードには、三菱マイコン機器ソフトウェア株式会社のPowerMedusa MU200-EA10を用いた。

- 開発ツールはALTERA MAX+PLUS2、およびSIIのVisual HDL for VHDLである。

- クロックタイム・ベースシミュレションにより、過渡応答を完全に再現できる。

- 以下の多くの知見を得られて大変有意義であった。

- 低回転から高回転まで全ての速度範囲でPLL速度ロックを達成できた。

- ディジタルオシロによる観測で、完全に位相同期も達成できることを確認した。

- 積分分解能の不足によるリップルの発生への対策を、オーバーサンプリング によって講じることができた。

- その他

機械学会関西学生卒業研究発表会(立命館大学(草津市))で発表、舞鶴高専学内学生表彰