平成 13 年度 舞鶴工業高等専門学校地域テクノセンター公開講座

# 「CAD による IC 回路設計と FPGA による実現 」

### 電子制御工学科 町田秀和

E-mail machida@maizuru-ct.ac.jp, TEL(FAX) 0773-62-8957

# 目次

| 1  | はじめに                               | 1 | 1  |

|----|------------------------------------|---|----|

| 2  | FPGA とは何か                          | ; | 2  |

|    | 2.1 開発の流れ                          | 2 | 2  |

|    | 2.2 開発装置                           | 4 | 1  |

|    | 2.2.1 ダウンロードケーブルの製作                | 5 | 5  |

|    | 2.2.2 FPGA 評価ボード(書き込み器)の製作         |   | 6  |

|    | 2.3 同期回路設計について                     |   | 8  |

| 3  | EDA ツールの操作演習入力からシミュレーションまで         |   | .0 |

|    | 3.1 組み合わせ論理回路                      | ( | 9  |

|    | デコーダとマルチプレクサの回路図入力                 |   |    |

|    | 3.2 順序回路                           | 2 | 8  |

|    | シンクロナイザの回路図入力とアップ・ダウンカウンタの VHDL 記述 |   |    |

| 4  | 任意周波数信号発生器の実現                      | 3 | 0  |

| 5. | おわりに                               | 3 | 0  |

### 1.はじめに

今日、電子制御機器のコントローラ等を実装する電子回路は、1 チップの専用 IC で実現されるのが主流になってきていますが、現実には、所望の応用に対して適当な IC が存在しなかったり入手が困難であることが多いという問題があります。

そこで、他社よりも速く製品化して利益をあげるいわゆる「タイムツーマーケット」を達成できるようになることを目指し、比較的大規模な書きこみ可能な IC である FPGA で所望の IC を実現する技法を習得します。そこでは、IC 回路設計用 CAD (EDA)である MAX+PLUS2 を利用し、信号発生器を実現する IC を設計した後、FPGA で実現するために書き込みケーブルおよび FPGA 評価ボードを製作し、実機実験を行う技術について講習します。

| ス・ 神座スプラユール |       |    |                 |    |  |  |  |

|-------------|-------|----|-----------------|----|--|--|--|

| 講習          | 講習日時  |    | 講義内容            | 講師 |  |  |  |

| 11月8日(木)    | 19:00 | ١. | 書きこみ用ケーブルの製作    | 町田 |  |  |  |

|             | 21:00 |    | EDA ツールの基礎      |    |  |  |  |

| 11 月 13 日   | 19:00 | 1  | 評価用 FPGA ボードの製作 | 町田 |  |  |  |

| (火)         | 21:00 |    | EDA ツールの応用      |    |  |  |  |

| 11 月 15 日   | 19:00 | 1  | 信号発生器の製作        | 町田 |  |  |  |

| (木)         | 21:00 |    |                 |    |  |  |  |

表1 講座スケジュール

### 2. FPGA とは何か?

FPGA(Field Programmable Gate Array)とは、その名前のとおり「現場で書き込み可能なゲートアレーIC」です。それでは一体、従来の IC によるディジタル回路の実現方法とどのように異なるかを表 2 で比較してみましょう。

|        | 従来の実現                         | FPGA による実現                   | FPGA のメリット                              |

|--------|-------------------------------|------------------------------|-----------------------------------------|

| 実現形態   | 74 シリーズなど小規模<br>IC の組み合わせ     | 1 チップに収まる                    | 信頼性の向上                                  |

| セキュリティ | 回路を読み取られてしまう。                 | 対策可能                         | 情報を盗まれない                                |

| 設計手段   | 紙と鉛筆                          | パソコン                         | パソコンで動作確認が行<br>える。                      |

| 設計方針   | しばしば非同期回路設計                   | 同期回路設計                       | パソコンの設計ツール<br>が使用できる。                   |

| 回路の流用  | 設計者にしか分かりにくい                  | モジュール(ライブラリ、IP<br>コア)として再利用可 | 設計管理が容易                                 |

| 実装     | ブレッドボードあるいは、<br>ユニバーサル基板に半田付け | FPGA 評価ボードを用意<br>すれば書き込みだけ   | 半田付け等不要、検証<br>だけに集中できる。                 |

| 入手容易性  | しばしば納期が遅れる。また<br>廃品種となることがある。 | 何度でも書き換えられるので、デッドストックにならない   | 納期、在庫のリスクを<br>回避できる。                    |

| 開発期間   | 設計、動作検証、部品の手配<br>に手間がかかりすぎる。  | パソコンだけですぐに取り<br>かかれる。        | タイムツーマーケットを<br>実現できる。                   |

| 回路の変更  | ほとんど不可能                       | 基板に実装したままで可能                 | 本来の機能を生かせる。                             |

| 書き込み装置 | 不要                            | 必要                           | 余分な回路が必要だが、<br>簡単である。またフラッシ<br>ュタイプもある。 |

表 2. FPGA とは何か

これらの特徴から FPGA を活用するキーポイントは次のとおりであることが指摘できます。

- 1.パソコンと設計ツール(CAD あるいは EDA)の操作法の習得すること。

- 2. FPGA評価ボードと、書き込み装置を用意すること。

- 3.同期回路設計をマスターすること。

それでは、一つづつ見ていきましょう。

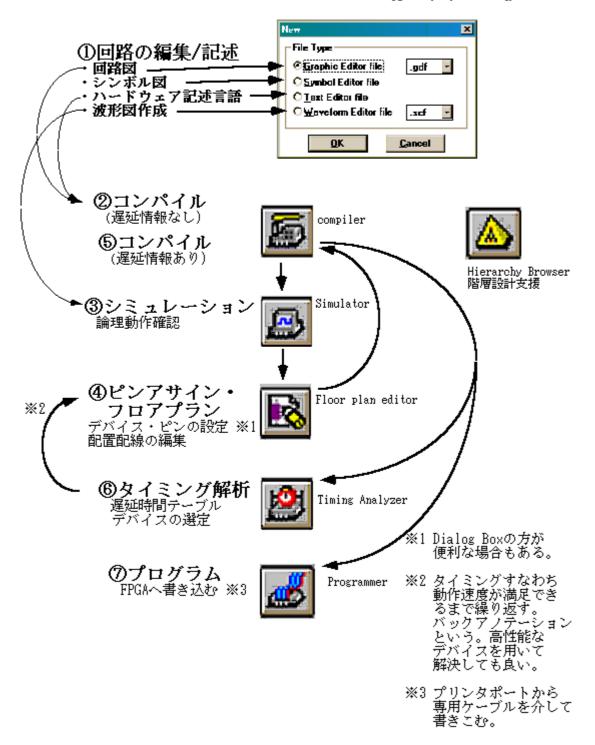

### 2.1 開発の流れ

FPGA の開発は専用の設計ソフトウェア EDA(Electronics Design Automation)ツールを用いて行います。現在では Web から入手でき、規模や機能を限定したものならほぼ無料で使用できます。次のページの**図1** に EDA ツールを用いた FPGA の開発の流れを示します。

# EDAツールによるFPGA設計の流れ

図 1 EDA ツールによる FPGA 設計の流れ

本講習会ではAltera社のFree版のMAX+PLUS2というEDAツールを用います。これは、 <a href="http://www.altera.com">http://www.altera.com</a> からダウンロードすることができます。この図の各アイコンは MAX+PLUS2 のものです。3 万ゲート規模の FPGA まで実際に開発することができます。 本校電子制御工学科 5 年生の CAD 演習 の授業で使用しています。

### 2.2 開発装置

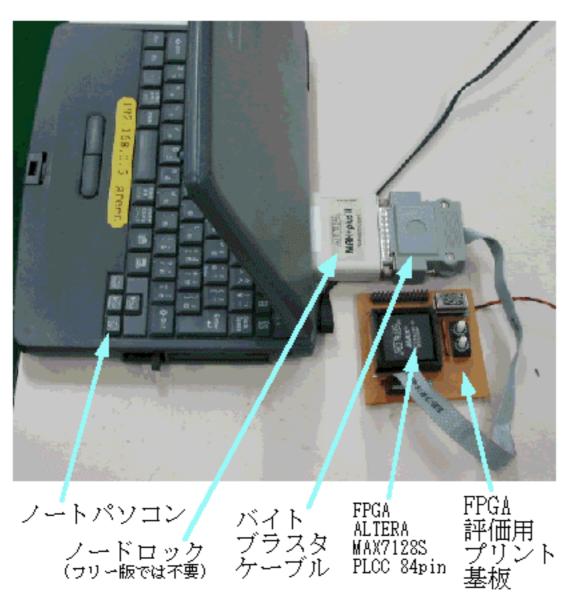

写真1に FPGA 開発装置の様子を紹介します。

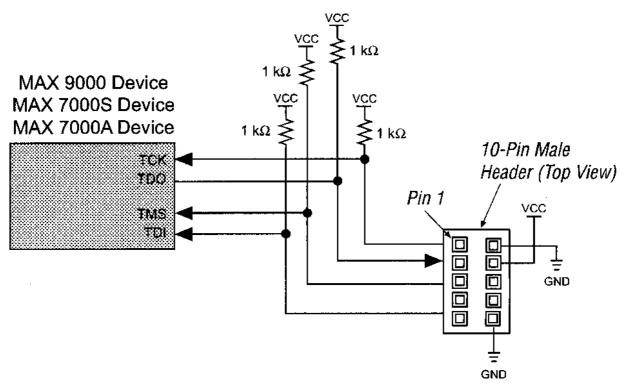

最近の FPGA は専用の書き込み器で書き込むのではなく、パソコンのプリンタポート(あるいは、シリアル、USB)から専用ケーブル(ダウンロードケーブルと呼ばれる)を介して、書き込まれます。また、FPGA はプリント基板に実装したままで書き込めます(In System Programming)。プログラミング時間はほんの数秒で終了します。

写真 1 FPGA 開発装置全景

なお、FPGA には S-RAM タイプ(例: FLEX10K)と EEP-ROM タイプ(例:MAX7000)があり、前者は電源を切れば回路内容が失われてしまうため、それを避けるためにはコンフィグレーション用のシリアル ROM が必要になります。ただし、S-RAM タイプの方が大容量の回路を実現できます。

## 2.2.1 ダウンロードケーブルの製作

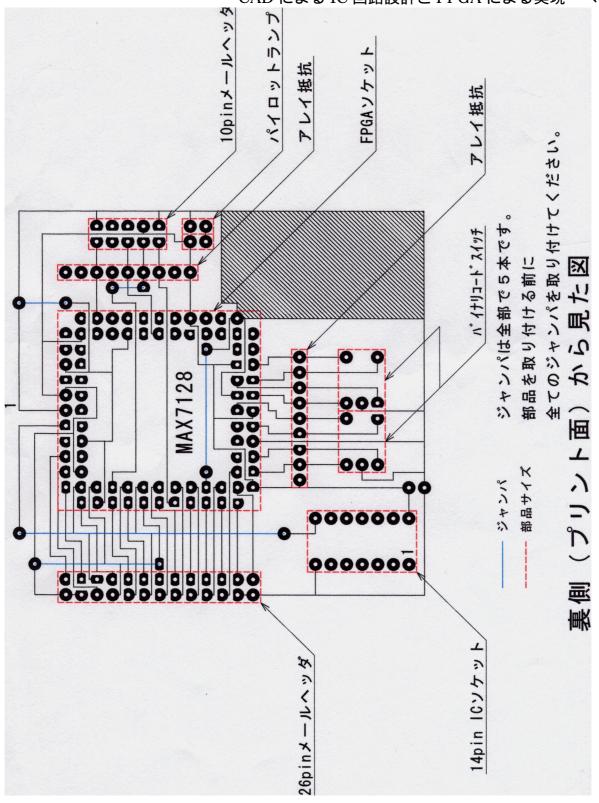

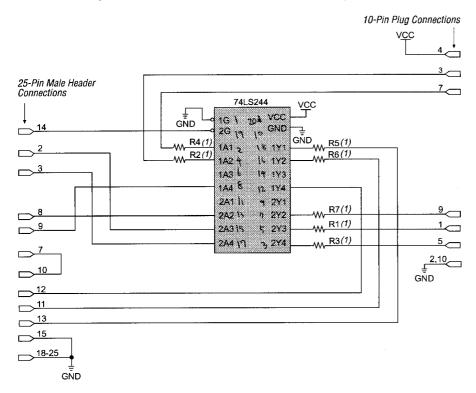

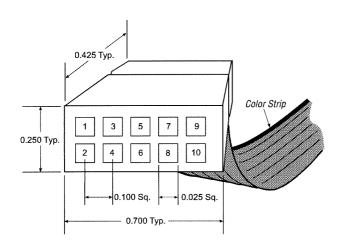

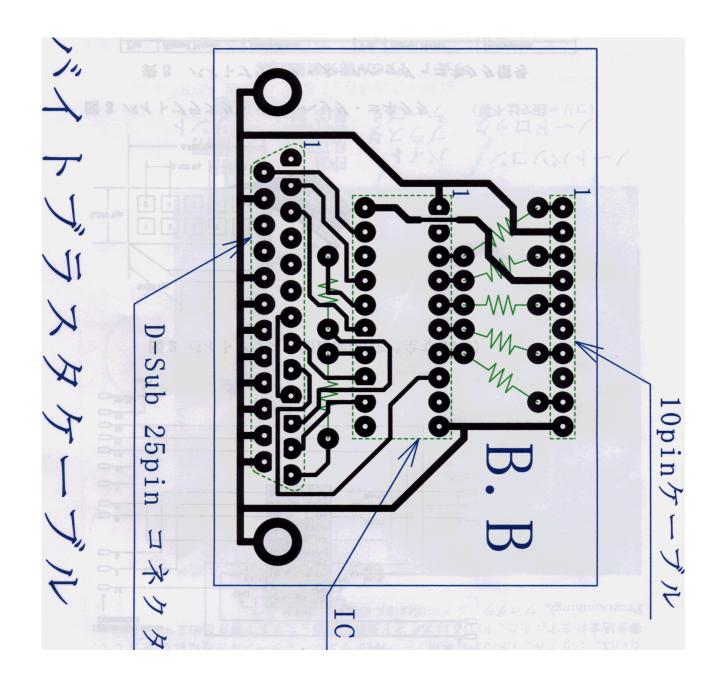

Altera 社から公開されている**図 2** よりダウンロードケーブル(バイトブラスタ)は簡単に 自作できます。本講習会では次ページ**図 4** のようにこの回路を試作します。

図2 バイトプラスタ回路図(抵抗は全て33)

図3 バイトプラスタ・メールヘッダ・コネクタ

表3 バイトプラスタ・メールヘッダ・コネクタ信号

| Pin | Signal Name | Description      | Pin | Signal Name | Description    |

|-----|-------------|------------------|-----|-------------|----------------|

| 1   | TCK         | Clock            | 6   | =           | No Connecnt    |

| 2   | GND         | Signal GND       | 7   | =           | No Connecnt    |

| 3   | TCO         | Data from device | 8   | -           | No Connecnt    |

| 4   | VCC         | Power supply     | 9   | TDI         | Data to device |

| 5   | TMS         | Control          | 10  | GND         | Signal GND     |

図4 バイトプラスタ基板実体配線図

## 2.2.2 FPGA 評価ボード(書き込み器)の製作

本講習会では Altera 社の MAX7128S という FPGA(CPLD)をターゲットとします。こ こでは、この FPGA の評価ボードを製作します。MAX7128S は 84 ピン PLCC ソケット タイプで、また EEP-ROM タイプなので一度書き込めば、電源を切っても、ソケットから 抜いても回路情報は消去されません。すなわち、この評価ボードは書き込みボードとして も活用することができます。 本講習会では次ページ図6のようにこの回路を試作します。

| PA THE STREET HIS INVESTIGATION OF THE PROPERTY OF THE PROPERT |    |               |    |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|----|--|--|--|--|

| 品名                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 個数 | 品名            | 個数 |  |  |  |  |

| プリント基板                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  | ヘッダピン 2列10pin | 1  |  |  |  |  |

| PLCC 84pin ソケット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  | ヘッダピン 2 列     | 1  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 26pin         |    |  |  |  |  |

| DIP 14pin ソケット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 水晶発振モジュール     | 1  |  |  |  |  |

| アレー抵抗 103×8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2  | 抵抗 470        | 1  |  |  |  |  |

| バイナリスイッチ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2  | LED 緑         | 1  |  |  |  |  |

表 4. FPGA 評価ボード部品表

表 5 MAX7128S ピンアサイン表

| 43 WAX11203 C27 3 1 2 1 2 |           |    |     |    |     |    |     |    |       |

|---------------------------|-----------|----|-----|----|-----|----|-----|----|-------|

| ピン                        | 名称        | ピン | 名称  | ピン | 名称  | ピン | 名称  | ピン | 名称    |

| 1                         | GCLR      | 21 | I/O | 41 | I/O | 61 | I/O | 81 | I/O   |

| 2                         | OE2/GCLK2 | 22 | I/O | 42 | GND | 62 | TCK | 82 | GND   |

| 3                         | Vcc       | 23 | TMS | 43 | Vcc | 63 | I/O | 83 | GCLK1 |

| 4                         | I/O       | 24 | I/O | 44 | I/O | 64 | I/O | 84 | OE1   |

| 5                         | I/O       | 25 | I/O | 45 | I/O | 65 | I/O |    |       |

| 6                         | I/O       | 26 | Vcc | 46 | I/O | 66 | Vcc |    |       |

| 7                         | GND       | 27 | I/O | 47 | GND | 67 | I/O |    |       |

| 8                         | I/O       | 28 | I/O | 48 | I/O | 68 | I/O |    |       |

| 9                         | I/O       | 29 | I/O | 49 | I/O | 69 | I/O |    |       |

| 10                        | I/O       | 30 | I/O | 50 | I/O | 70 | I/O |    |       |

| 11                        | I/O       | 31 | I/O | 51 | I/O | 71 | TDO |    |       |

| 12                        | I/O       | 32 | GND | 52 | I/O | 72 | GND |    |       |

| 13                        | Vcc       | 33 | I/O | 53 | Vcc | 73 | I/O |    |       |

| 14                        | TDI       | 34 | I/O | 54 | I/O | 74 | I/O |    |       |

| 15                        | I/O       | 35 | I/O | 55 | I/O | 75 | I/O |    |       |

| 16                        | I/O       | 36 | I/O | 56 | I/O | 76 | I/O |    |       |

| 17                        | I/O       | 37 | I/O | 57 | I/O | 77 | I/O |    |       |

| 18                        | I/O       | 38 | Vcc | 58 | I/O | 78 | Vcc |    |       |

| 19                        | GND       | 39 | I/O | 59 | GND | 79 | I/O |    |       |

| 20                        | I/O       | 40 | I/O | 60 | I/O | 80 | I/O |    |       |

表 6 試作 FPGA 評価ボードの外部接続用ピンアサイン

|    | -V    | <b>M</b> | <u> </u> |    | 11 327707 | ., |       |

|----|-------|----------|----------|----|-----------|----|-------|

| ピン | 名称    | ピン       | 名称       | ピン | 名称        | ピン | 名称    |

| 1  | GND   | 8        | I/O58    | 15 | I/O67     | 22 | I/O76 |

| 2  | I/O55 | 9        | I/O61    | 16 | I/O68     | 23 | Vcc   |

| 3  | GND   | 10       | I/O60    | 17 | I/O69     | 24 | I/O75 |

| 4  | I/O54 | 11       | I/O63    | 18 | I/O70     | 25 | Vcc   |

| 5  | I/O52 | 12       | I/O64    | 19 | I/O73     | 26 | I/O79 |

| 6  | I/O56 | 13       | I/O65    | 20 | I/O74     |    |       |

| 7  | I/O57 | 14       | Vcc      | 21 | I/O77     |    |       |

表 6b バイナリロータリスイッチ ピン番号

| SW 桁 | 上位 H | 下位 L |

|------|------|------|

| 1    | 40   | 49   |

| 2    | 41   | 51   |

| 4    | 39   | 45   |

| 8    | 37   | 44   |

図 5. メールヘッダ部分回路図

図 6 FPGA 評価ボード実体配線図(最終ページにあります。)

# 2.3 同期回路設計について

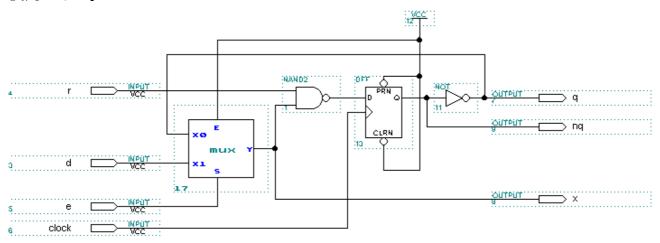

ASIC の設計では、フリップフロップを使用する順序回路は、すべて**システムクロック の立ち上がり**に同期設計すべきである。同期設計ならば、タイミング計算も容易であり、無理がないので高速化も達成しやすい。もちろん、設計自体も統一的な指針で望める。

**図7** は順序回路の基本的な機能である、データ、リセット、イネーブルが全てクロックの立ち上がりに同期して行なえる基本回路(プリミティブ回路)である。

同期回路の特徴は、クロック線が全てのフリップフロップに共通(グローバル)で、途中に ゲート等が入らない(ゲーテッドクロック)ことである。 なお、クロック信号の遅延を避けるための配線(クロックツリー)は EDA ツールで評価できる。

| ~~ ' |       | · <del></del> |         |

|------|-------|---------------|---------|

| 入出力  | 機能    |               | 信号本数(値) |

| 入力   | クロック  | clock         | 1       |

|      | データ   | d             | 1       |

|      | イネーブル | · e           | 1       |

|      | リセット  | r             | 1       |

| 出力   | 状態    | q             | 1       |

|      | 反転状態  | nq            | 1       |

表7 同期回路の基本回路入出力端子

表8 同期回路の基本回路の真理値表

|       | 入 | 出 | カ |   |    |

|-------|---|---|---|---|----|

| clock | d | е | r | q | nq |

|       | × | × | 0 | 0 | 1  |

|       | × | 0 | 1 | q | nq |

|       | 0 | 1 | 1 | 0 | 1  |

|       | 1 | 1 | 1 | 1 | 0  |

注意:E+MAX の D-F/F プリミティブの非同期プリセット(PRN), リセット(CLRN)は使用しない。

図7 同期回路のプリミティブ (ファイル名 sprim.gdf)

### 3.EDA ツールの操作演習

### 3.1 組み合わせ論理回路

### 課題1 2入力4出力イネーブル付デコーダ

### 手順1 開発するシステムの機能の確認

デコーダとは、**入力のある組み合わせ(コード)**が与えらた時に、**出力のどれか一つだけ**が'1'になる組み合わせ論理回路である。またコントロール入力端子として**許可(イネーブル)入力**がある。イネーブル入力が'0'の時は入力(コード)の値に関わらず、出力は全て'0'となる。 すなわち、汎用的なデコーダの入出力端子は表 9 のとおりである。

表 9 デコーダの入出力端子

| 入出力 | 機能    | 信号本数(値) |  |  |  |  |

|-----|-------|---------|--|--|--|--|

| 入力  | 入力コード | n       |  |  |  |  |

|     | イネーブル | 1       |  |  |  |  |

| 出力  | 選択出力  | 2 の n 乗 |  |  |  |  |

表 10 デコーダプリミティブ真理値表

| 入 | 力 | 出力 |    |  |

|---|---|----|----|--|

| e | X | y1 | y0 |  |

| 0 | × | 0  | 0  |  |

| 1 | 0 | 0  | 1  |  |

| 1 | 1 | 1  | 0  |  |

表 11 2-4 デコーダ真理値表

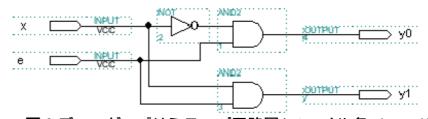

図8デコーダ・プリミティブ回路図(ファイル名 dec.gdf)

|   | 入力 | ]  |    | 出  | 力  |    |

|---|----|----|----|----|----|----|

| e | x1 | x0 | y3 | y2 | y1 | y0 |

| 0 | ×  | ×  | 0  | 0  | 0  | 0  |

| 1 | 0  | 0  | 0  | 0  | 0  | 1  |

| 1 | 0  | 1  | 0  | 0  | 1  | 0  |

| 1 | 1  | 0  | 0  | 1  | 0  | 0  |

| 1 | 1  | 1  | 1  | 0  | 0  | 0  |

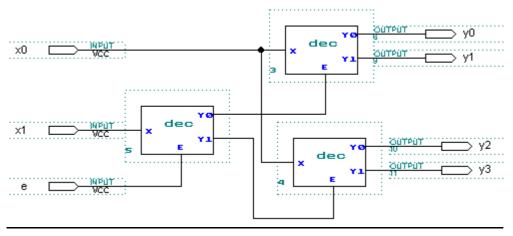

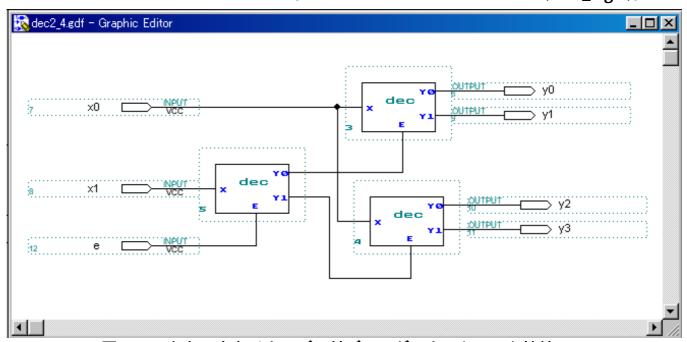

図 9 デコーダ・ネットワーク接続回路図 (ファイル名 dec2\_4.gdf)

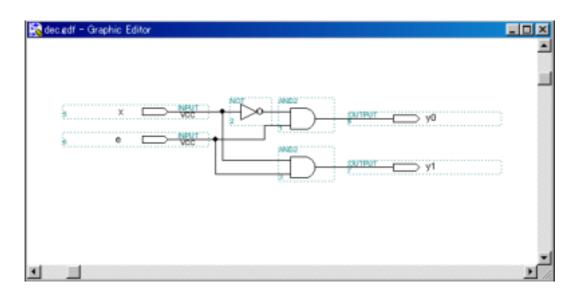

# 手順2 基本回路(プリミティブ)の回路図入力

図10のデコーダ・プリミティブの回路図を作成する。

図 10: デコーダのプリミティブ

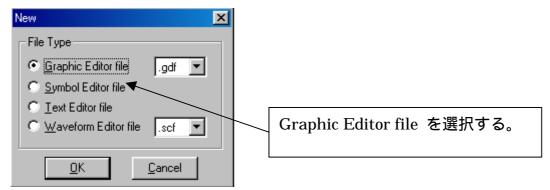

## ステップ1 グラフィックエディタの起動

図 11 の新規作成ボタンを左クリックして、図 12 のように Graphic Editor File(gdf)を選 択して、OK をクリックする。図 10 の Untitled 1-Graphic Editor という画面が出てくる。

図 11:新規作成

図 12: Graphic Editor File の選択

### <u>ステップ 2 部品シンボルのライブラリからの取り出し</u>

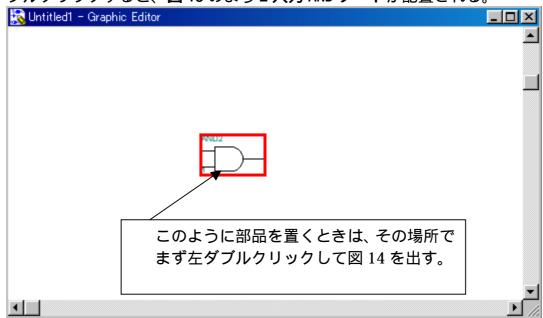

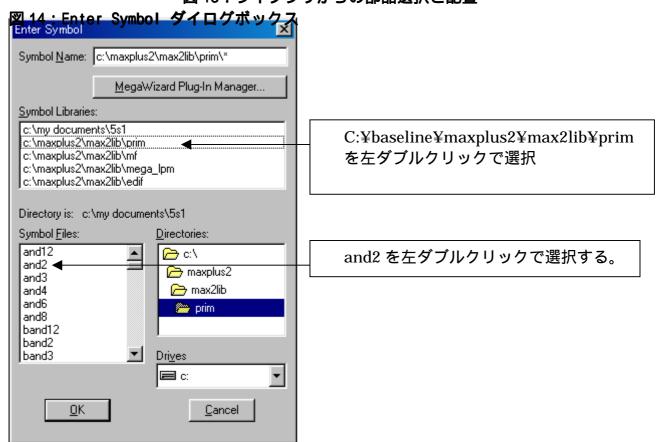

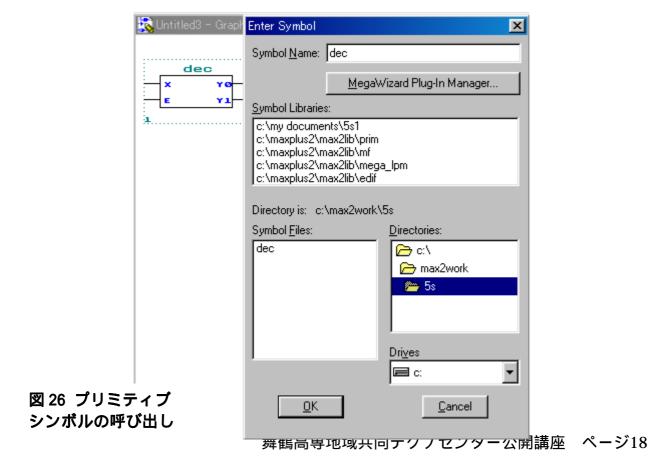

まず AND **ゲート**を配置する。**図 13** ようにマウスカーソルを Untitled 1-Graphic Editor 画面の適当な場所に移動して左ダブルクリックする。

そうすると、**図 14** のような Enter Symbol ダイアログボックスが出てくる。そこで、Symbol libraries 欄の c:\\$baseline\\$maxplus2\\$max2ib\\$prim をダブルクリックする。Symbol Files 欄の中に and12,and2,and3,...などが見えてくる。そこで、and2 を選択し、ダブルクリックすると、**図 13** のよう 2 入力 AND ゲートが配置される。

図 13:ライブラリからの部品選択と配置

舞鶴高専地域共同テクノセンター公開講座 ページ12

### <u>ステップ3 部品のコピー&ペーストによる配置</u>

デコーダ・プリミティブを構成するためには、and2,not,input と output の 4 種類が必要である。そこで、それぞれを 1 個づつ**ステップ** 2 のやり方で配置する。

それから、<u>同じ部品</u>を選択したい場合は<u>該当の部品を左クリック</u>して、<u>コピー(Ctrl+c)</u> して、 <u>ペースト(Ctrl+v)</u>すると**ステップ 2** のやり方を繰り返さなくても良い。 このようにして、**図 15** のように全ての部品を配置する。

ところで、**部品を移動**するには、その部品に左クリックしたまま、画面内(Untitled 1-Graphic Editor)のお好みの場所へ移動(**ドラッグ**)させる。また、全図形またはある部分を移動したい場合は<u>移動したい部分の左上から右下までドラッグして離して一旦範囲を指</u>

図 15:全部品の配置

# ステップ4配線

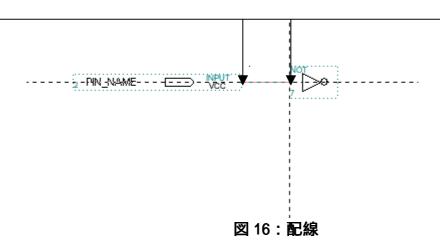

図8のように部品間を配線をする。配線は図16のように、その部品の端子を左クリックして、目的の部品の端子までドラッグして離す。ただし、配線作業をするときは画面を拡大した方ががやりやすい。

**ポイント1** ほんとうに**配線できているかどうか**は、部品を少しドラッグしてみて配線がいっしょに移動すれば大丈夫と確認できる。見た目は接続されてるように見えても、 実際にはつながっていない場合があるので注意せよ。

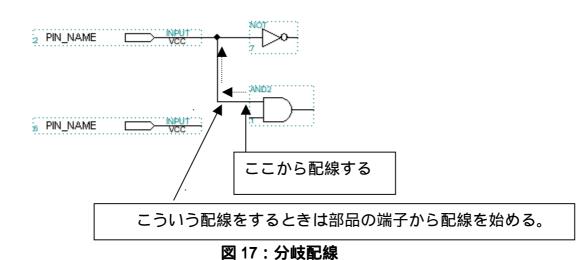

**ポイント2** 図 17 に示すように**配線の途中から**さらに配線したい場合でも、<u>目的の部品の</u> <u>端子から配線</u>する。また曲がり配線(L 配線)をする場合は直線ごとに配線する。 (図 14 に参照)

<u>ポイント3</u> 配線間違いがあれば、間違った配線の部分をクリックして、'Delete' キーを押す と間違っている部分が削除できる。要らない部品の削除も同様である。

ある部品の端子から他の部品の端子まで左クリックし、ドラッグして、離すと部品 配線ができる。このときマウスカーソルは点線の十字となる。

2 PIN NAME NPUT 3ND2

3 PIN NAME NPUT 3ND2

3ND2

配線は部品の端子から引っ張り、一度、曲がるところで止め(クリックを離す)、そこからもう一度ドラッグして再び配線する。

図 18:L 配線

## ステップ 5 入出力端子名を名付ける

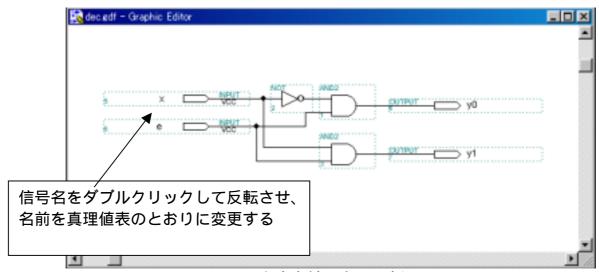

図19のように、<u>入出力端子名の場所をダブルクリック</u>して、黒く反転させ、 <u>手順1の真理値表どおりの名前</u>に変更する。変更後、エンターキーを押すと、 次の端子の名前変更に自動移動する(自動移動は、入力端子あるいは出力端子についてだけ)。

図 19:入出力端子名の更新

### ステップ6回路図の保存

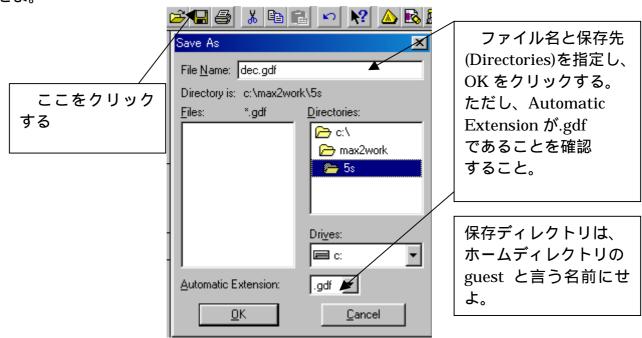

図8の回路図が完成したら、配線を確認してから、図20の手順で保存する。 保存先は自分のホームディレクトリ、ファイル名は<u>手順1で指定しているdec.gdf</u> とせよ。

図 20: 図形の保存

舞鶴高専地域共同テクノセンター公開講座 ページ15

# 手順3 プリミティブのシンボル(部品記号)の編集

## ステップ7 プリミティブのシンボル作成

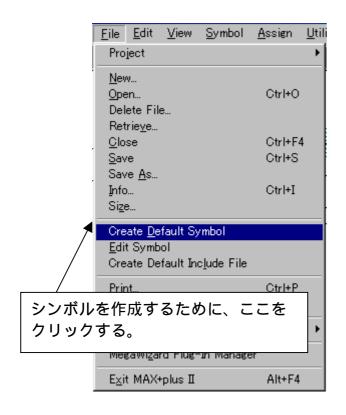

完成した**図8**のプリミティブ回路自体を一つの部品シンボルとする**。図21**に示すように、 メニューの File の Create Default Symbol にクリックする。この操作は一瞬で終わる。

これでグラフィックエディタウィンドウを右上の×ボタンをクリックして閉じる。

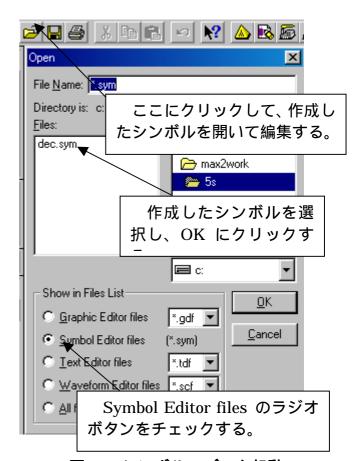

## ステップ8 シンボルエディタの起動

作成したシンボルを編集するためにシンボルエディタを起動する。**図 22** に示すように、**ファイルオープン**して、**Symbol Editor files の欄にチェック**が付いていることを確認する。そして、<u>先ほど作成したシンボル名(dec.sym)</u>を選択し、OK をクリックすると、**図 23** に示すようなシンボルが表示される。

図 22:シンボルエディタ起動

### ステップ8 シンボルの編集

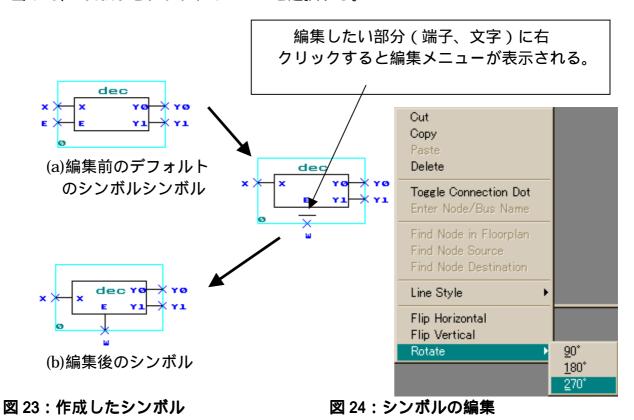

図 23 のシンボルのピン(入出力端子)の位置はデフォルト位置になっている。

これを手順1のネットワーク接続回路のようにピンの位置になるように編集する。

シンボルの編集(ピン位置または文字位置)は、編集したい部分を右クリックすると、編集メニューが出てくる。そのメニューを利用して、シンボルの編集ができる。 ここでは、次のように操作する。

内側の黒色の箱内の左側にある E という文字をドラッグして下に移動する。 外側の空色の箱の左縦線上にある x というシンボルをドラッグして下に移動する。 と を接続していた横向きの線を図の位置にドラッグし、マウスの右メニューを 出して、Rotate をクリックし 270°を選択する。

同様にして、端子xの位置と、シンボル名 dec の位置を図 23(b)のように編集する。

シンボルの編集が完了すれば、**セーブボタンで上書き保存**する。またシンボルエディタウィンドウの右上の**×ボタン**をクリックして閉じる。

# 手順4プリミティブのネットワーク接続によるシステム回路図入力

### ステップ9 ネットワーク回路図の作成

ネットワーク回路の作成は**手順2**のプリミティブの作成と全く同様である。ただし、作成したシンボルを部品として配置する場合は**図21**のように Symbol Libraries のところにホームディレクトリを指定してから選ぶ。 保存名は手順1で指定している(dec2\_4.gdf)。

図 25:2 入力 4 出力イネーブル付デコーダのネットワーク接続

# 手順5 コンパイル

### ステップ 10 プロジェクトの登録

これから、作成した回路をコンパイルする作業にはいる。まず、Ctrl+Shift+Jキーを 押す。これは作成した**現在の回路をプロジェクトに登録**することを意味する。メニュー からプロジェクトを登録することもできる。(メニューの File Project Set Project to Current File を選択する。)

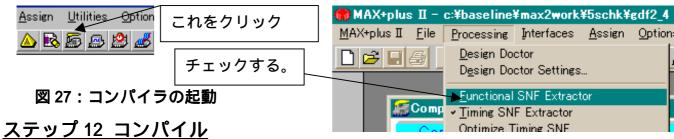

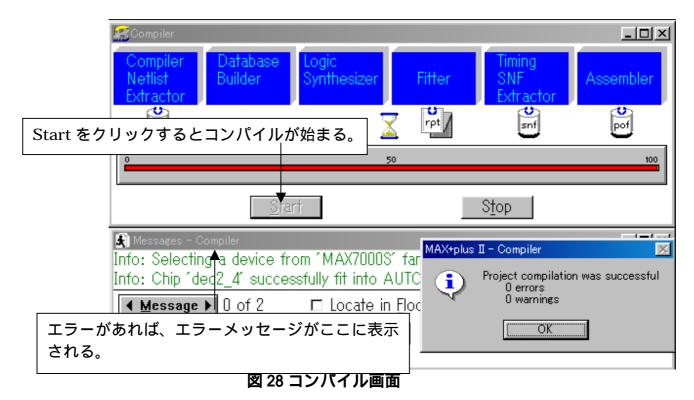

# ステップ 11 コンパイラの起動

コンパイラの起動は図27の工場の形のボタンをクリックするか、メニューMAX+PLUS2 Compiler を選択する。また Processing メニューの Function..をチェックする。

図 28 の Start をクリックするとコンパイルが始まる。エラーがある場合は、Messages 画面にエラーが表示される。エラーmessage をクリックして、間違っているところが表示 される。間違っている部分を訂正し、セーブしてから、再びコンパイルする。

配線がつながっていないことをはじめ、ピン名を指定していないことなどがエラーの 主な原因となる。配線をする際に、画面を拡大することがポイントである。

舞鶴高専地域共同テクノセンター公開講座 ページ19

# 手順6 シミュレーション

コンパイル過程がエラーなく終了したら、本回路のシミュレーションをやってみよう。 シミュレーションによって、本回路が正しく動作しているかどうか確かめることができる。

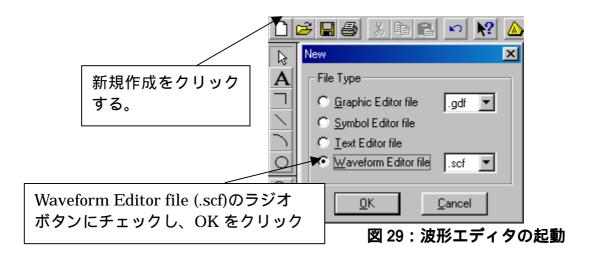

# ステップ 13 波形エディタの起動

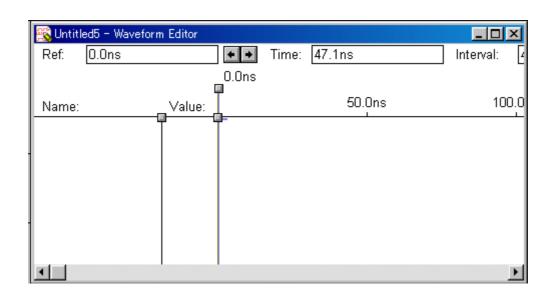

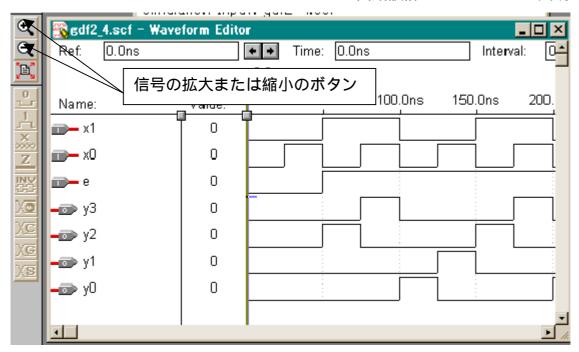

**図 29** に示すように新規作成から、Waveform Editor file(.scf)を起動する。**図 30** のように Waveform Editor の画面が表示される。

図30: Waveform Editor の画面

### ステップ 14 入出力端子情報の取り込み

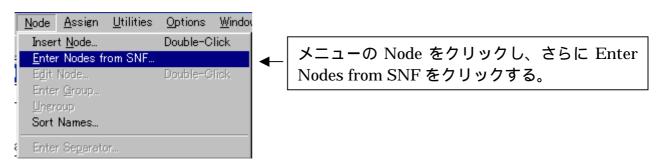

図 31 のようにメニューの Node をクリックし、Enter Nodes from SNF を選択する。

図 31:.snf ファイルから入出力の挿入

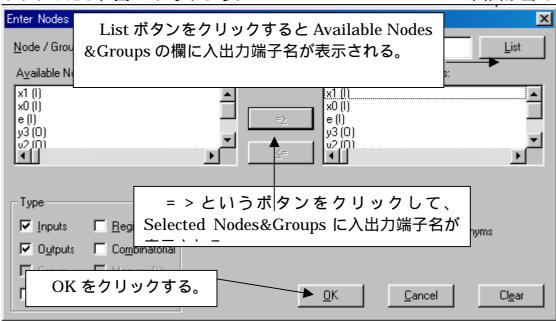

そうすると**図 32** が現れるので、図中の手順で入出力端子情報を取り込む。OK ボタンをクリックしたら、**図 33** に示すように Untitled Waveform Editor の画面が出てくる。

図 32:シミュレーションに表示される入出力端子名の選択

図33:シミュレーションに用いる入出力信号

舞鶴高専地域共同テクノセンター公開講座 ページ21

## ステップ 15 入力波形の編集

ネットワーク回路のシミュレーションする際に、テスト入力信号パターンを与える。 このテスト入力信号パターンは、**手順1**で与えられた**真理値表**に基づくものとする。

### ステップ 15-1 全ての組み合わせが必要な入力の編集

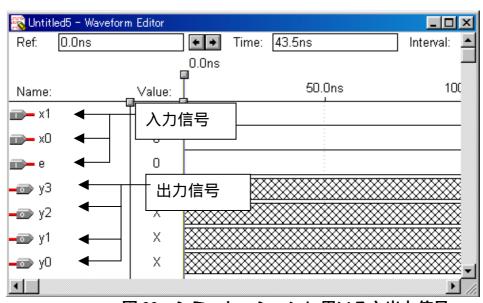

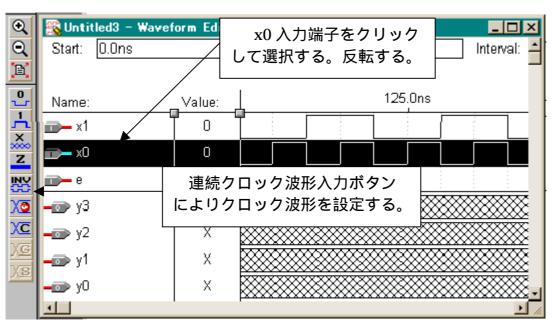

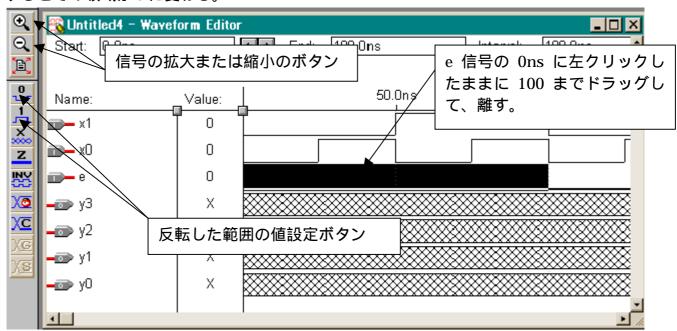

まず、図34のように入力信号x0とx1とeの波形を作成する。これは真理値表どおりに、x0とx1とeの全ての組み合わせについて与える必要があるので、連続的な方形波として入力する。

### X0 の入力

図 35 のように、メニューの Option Grid Size で Grid Size を <u>25.0ns</u>に設定する。 WaveForm Editor ウィンドウの Name の下の x0 の端子をクリックして、x0 全体を選択する。

WaveForm Editor ウィンドウの左側の時計マークの周期的パルス入力ボタンをクリックすると、全時間にわたって、周期  $50ns(25ns \times 2)$ の方形派が設定される。

### x1 の入力

**x1** も **x0** と同様に入力する。ただし、 で **Grid Size** を 50.0ns に設定する。この 2 倍づつに設定するのが、全ての組み合わせを入力するコツである。

図34:全ての組み合わせが必要な入力の編集

図 35: グリッドサイズの設定

### ステップ 15-2 ある特定の時間だけ'0'か'1'を指定する信号の入力

例えば、図 36 に示すように e(イネーブル)信号の最初の 50ns までは'0'状態に設定するには、e 端子をクリックし、全体を反転させ、編集メニューの'1'のボタンをクリックして、全体を 1 に設定した後で、0ns の時点から 100ns の時点まで、左ドラッグして離す。すると e 信号の 0ns から 100ns までの領域が黒くなり、編集メニューの'0'のボタンをクリックするとその領域が'0'に変わる。

図 36:ある特定の時間だけ'0'か'1'を指定する信号の入力

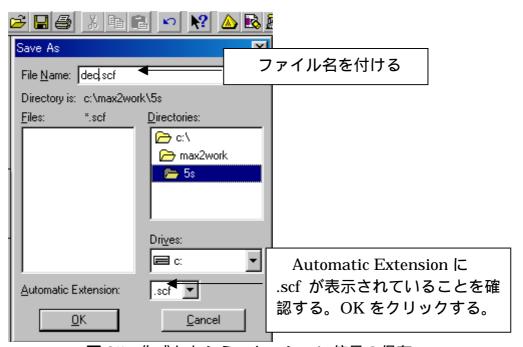

## ステップ 16 入力波形の編集

入力信号が編集できたら、図 37 のようにして.scf ファイルとして保存する。

図37:作成したシミュレーション信号の保存

## <u>ステップ 17 シミュレーションの実行と確認</u>

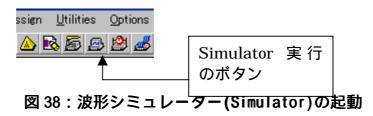

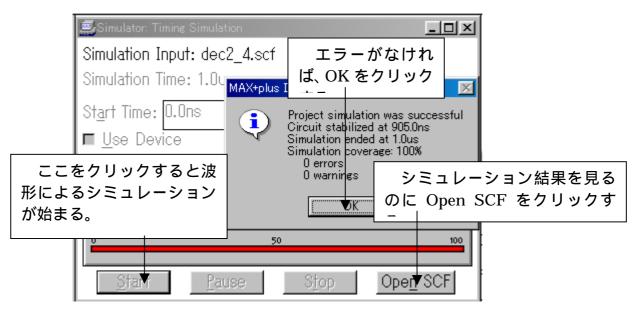

図 38 に示すようにシミュレーションボタン(Simulator)をクリックすると、図 39 のような画面(Simulator Timing Simulation)が表示される。

その画面の Start ボタンをクリックする。

エラーが発生しなければ、Max+plus -Simulator の OK ボタンをクリックする。

波形シミュレーションの結果を見るために、Simulator Timing Simulation 画面の Open SCF ボタンをクリックすると、図 40 のような画面が表示される。これは本回路のシミュレーション結果である。真理値表の出力結果と合致していることを確認する。

図 39: Simulator 画面

エラーが表示される場合は、エラー・メッセージに従い、エラーを修正する。

もし、シミュレーション結果が真理値表の結果と異なれば、もう一度、回路を見直す こと。

図 40:シミュレーション結果

シミュレーション結果を観測するには左の虫眼鏡のボタンで縮小して見やすくすれば良い。

# ステップ 18 ピンアサイン

シミュレーションが成功すれば、Assign Device でターゲット FPGA を選び、 Assign Pin/Location/Chip から図 41 のようにピン番号に入出力信号を割り振る。

| Pin/Location/Chip                                                                                                    | ×                       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|

| Top of Hierarchy: c:\eda\max2work\sok2001\dec2_4n.gdf                                                                |                         |  |  |  |

| Node Name:                                                                                                           | <u>0</u> K              |  |  |  |

| Chip Name: dec2_4n  ▼                                                                                                | <u>C</u> ancel          |  |  |  |

| Chip Resource Pin Type (Only for                                                                                     | Search                  |  |  |  |

| Special Cases):                                                                                                      |                         |  |  |  |

| O LC:                                                                                                                | Assign De <u>v</u> ice  |  |  |  |

| C LAB:                                                                                                               | Show Buried Assignments |  |  |  |

| Anywhere on this Chip                                                                                                | -                       |  |  |  |

| Existing Pin/Location/Chip Assignments:    e > chip = dec2_4n; Input Pin = 45                                        | Sort By                 |  |  |  |

| x0 > chip = dec2_4n; Input Pin = 49<br>x1 > chip = dec2_4n; Input Pin = 51                                           | Node Name               |  |  |  |

| y0 > chip = dec2_4n; Output Pin = 52                                                                                 |                         |  |  |  |

| y1 > chip = dec2_4n; Output Pin = 57<br>y2 > chip = dec2_4n; Output Pin = 61<br>y3 > chip = dec2_4n; Output Pin = 63 |                         |  |  |  |

| Delete                                                                                                               |                         |  |  |  |

| _                                                                                                                    |                         |  |  |  |

図 41: ピンアサイン

## ステップ 18 プログラミング(書き込み)

ピンアサインが済めばもう一度コンパイルする。そして、速度的に問題がなければ、いよいよ FPGA に回路を書き込む。パソコンのプリンタポートからバイトブラスタケーブルを介してターゲットの FPGA ボードに接続し、MAX+PLUS2 Programming から**図 42** の Programのボタンを押す。わずか数秒で書き込みは終了する。

図 42: プログラム

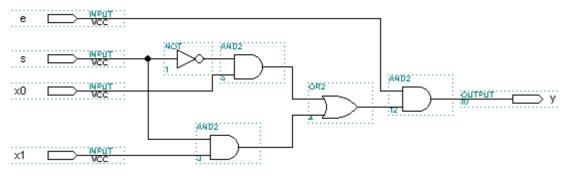

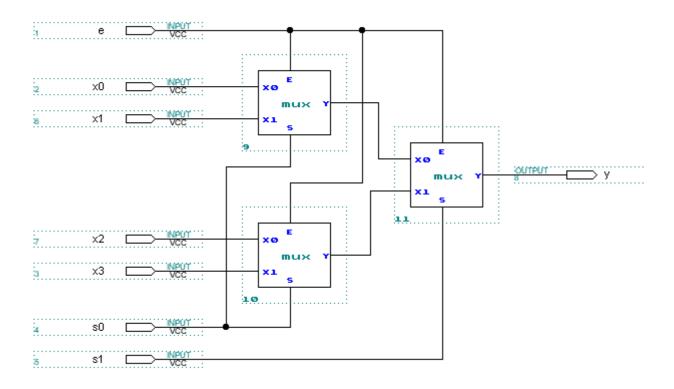

# 課題2 4入力1出力マルチプレクサ

# 手順1 開発するシステムの機能の確認

マルチプレクサとは 2 の n 乗.対.1 の切り替えスイッチである。このスイッチの切り替えのための n 本のコントロール入力端子を**セレクト入力**という。また**イネーブル入力**はこれが'0'の時は、入力がいかなる値であっても、出力が'0'となる。

すなわち、汎用的なマルチプレクサの入出力端子は以下のとおりである

| 入出力 | 機能     | 信号本数(値) |

|-----|--------|---------|

| 入力  | 入力信号   | 1       |

|     | セレクト入力 | n       |

|     | イネーブル  | 1       |

| 出力  | 分岐選択出力 | 2 の n 乗 |

表 12 マルチプレクサの信号

表 13 マルチプレクサ基本回路真理値表

|   | 入 力 |    |    |   |  |

|---|-----|----|----|---|--|

| е | s   | x1 | x0 | у |  |

| 0 | ×   | ×  | ×  | 0 |  |

| 1 | 0   | 0  | ×  | 0 |  |

| 1 | 0   | 1  | ×  | 1 |  |

| 1 | 1   | ×  | 0  | 0 |  |

| 1 | 1   | ×  | 1  | 1 |  |

図 42 マルチプレクサ基本回路(プリミティブ) (ファイル名 mux.gdf)

表 14 4-1 マルチプレクサネットワーク接続 ファイル名 mux41.gdf

|   | 入 力 |    |            |    |    | 出力 |    |

|---|-----|----|------------|----|----|----|----|

| е | s1  | s0 | х3         | x2 | x1 | x0 | у  |

| 0 | ×   | ×  | ×          | ×  | ×  | ×  | 0  |

| 1 | 0   | 0  | x3         | x2 | x1 | x0 | x0 |

| 1 | 0   | 1  | x3         | x2 | x1 | x0 | x1 |

| 1 | 1   | 0  | <b>x</b> 3 | x2 | x1 | x0 | x2 |

| 1 | 1   | 1  | х3         | x2 | x1 | x0 | x3 |

図 43 4-1 マルチプレクサネットワーク接続 ファイル名 (mux41.gdf)

# 3.2 順序回路

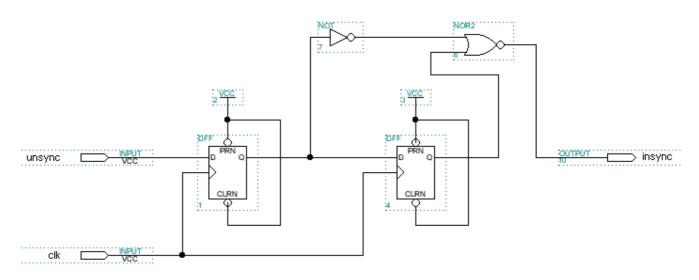

# 課題3 シンクロナイザの回路図入力

## 手順1 開発するシステムの機能の確認

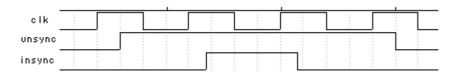

**シンクロナイザ**すなわち同期化器とは、クロックの立ち上がりに非同期な入力……例えば人間のスイッチ入力を同期化させる順序回路である。

この場合、同期化出力は、図のように非同期入力が 1 になった直後のクロック立ち上が リで 1 となり、その次の立ち上がりで 0 に戻る。このとき、同期化出力がクロック立ち上 がりで 1 になっているのは、0 に戻るときであることに注意が必要である。このことは、E+MAX のシミュレーションで確認できる。

| - TC 10 | <b>役 10</b> フラドロティラの八田/J旧 5 |         |   |  |  |

|---------|-----------------------------|---------|---|--|--|

| 入出力     | 機能                          | 信号本数(値) |   |  |  |

| 入力      | クロック                        | clk     | 1 |  |  |

|         | 非同期入力                       | unsyunc | 1 |  |  |

| 出力      | 同期化出力                       | insyunc | 1 |  |  |

表 15 シン k ロナイザの入出力信号

図 44 シンクロナイザの基本回路(プリミティブ) (ファイル名 sync.gdf)

図 45 シンクロナイザのシミュレーション結果

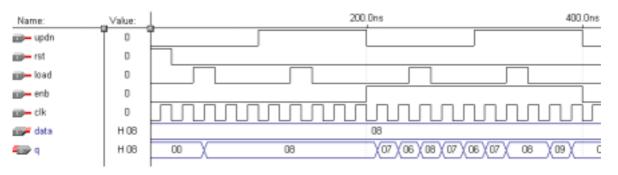

# 課題 4 アップダウンカウンタの VHDL 記述

複雑な順序回路の回路図を作図するのは相当の知識が必要です。

ここでは、ハードウェア記述言語 VHDL によるアップダウンカウンタの記述について説明します。 VHDL とは米国国防総省で規格化された現在最も標準的なハードウェア記述言語の一つです。VHDL の仕様は大変幅広く、とても全部を把握することは不可能ですが、FPGA で実現できる程度の文法であれば、数週間で学習することも可能です。

```

UDCNT8

LOAD

DATA[7..0] Q[7..0]

UPDN

ENB

RST CLK

```

### 図 46 カウンタの代表的なシンボル

```

1 library IEEE:

2 use IEEE.std_logic_1164.all;

3 use IEEE.std_logic_unsigned.all;

5 entity udcnt8 is

6

port( clk,rst,enb,updn,load : in std_logic;

data: in std_logic_vector (7 downto 0);

q : out std_logic_vector (7 downto 0));

9 end udcnt8;

10

11 architecture RTL of udcnt8 is

12 signal reg:std_logic_vector (7 downto 0);

13 begin

14

q <= reg;

process (clk) begin

15

if (clk'event and clk='1') then

16

17

if (rst='1') then

18

reg <= (others => '0');

elsif (load='1') then

19

20

reg <= data;

elsif (enb='1') then

21

22

if (updn='1') then

23

reg <= reg+'1';

24

else

25

reg <= reg-'1';

26

end if:

27

end if:

28

end if:

end process;

30 end RTL;

```

図 47 アップダウンカウンタのシミュレーション例

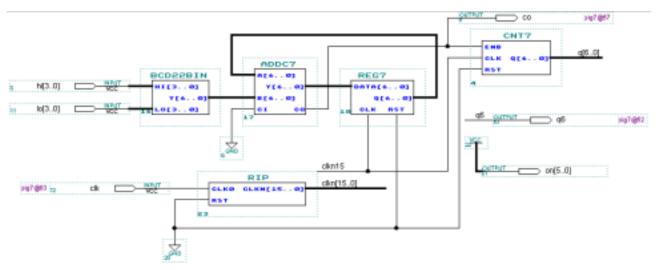

# 4.任意周波数信号発生器の実現

最後に、任意の周波数を発生できる発振器を実現してみる。すなわち、入力としてディジタル・バイナリ・スイッチで設定した周波数の方形波を出力する回路である。これは、V/F コンバータとしていろいろな用途に使用できる。

このようないわゆる「周波数シンセサイザ」は PLL(Phase-Locked Loop)で実現するのが一般的であるが、ここではもっと簡単に 変調器の構成により、開ループで実現する。 図 48 にその回路図を示す.詳細については講義中に解説する。

図 48 任意周波数発生回路

# 5.おわりに

CAD(EDA)ツールによる IC の設計と FPGA による実現について、一通りの作業手順を紹介しました。踏まなければならない手順は数多いのですが、一度経験してしまえば、きっと思ったより簡単であると感じてもらえたのではないでしょうか。

最近では、巷のパーツショップの少なくなり、小口の IC を入手するのは困難になってきています。そこで、このように FPGA で実現できればそのようなリスクを避けることができます。それよりも、ユーザ自身が新しい発想で IC を実現するということが、現実のものとなってきたということです。実際に、FPGA はもう最新のネットワーク機器内に数多く使用されており、大きな評価を得ています。

ただ、この分野は技術の進歩が本当に日進月歩であるため、インターネットや専門雑誌 (CQ 出版社、DESIGN WAVE MAGAZINE)等で情報収集を続けることが大変重要です。 この公開講座をきっかけに、今後、制御系や IC 開発について技術的なご相談がございましたら、またぜひ舞鶴高専地域共同テクノセンターまでご連絡をお待ちしています。

# 付録 ピンアサインと実験条件

# 1. デコーダ

表 A1 ピンアサイン 表 A2 実験条件

| - TC 711   |      |

|------------|------|

| 信号名        | ピン番号 |

| e          | 45   |

| x0         | 49   |

| <b>x</b> 1 | 51   |

| y0         | 52   |

| y1         | 57   |

| y2         | 61   |

| y3         | 63   |

| SW入力 | 2 進数値   | 反転信号値   | 出力信号値       | LED 点滅      |

|------|---------|---------|-------------|-------------|

| L    | e,x1,x0 | e,x1,x0 | y3,y2,y1,y0 | y3,y2,y1,y0 |

| 0    | 000     | 111     | 1000        | 0111        |

| 1    | 001     | 110     | 0100        | 1011        |

| 2    | 010     | 101     | 0010        | 1101        |

| 3    | 011     | 100     | 0001        | 1110        |

| 4    | 100     | 011     | 0000        | 1111        |

| 5    | 101     | 010     | 0000        | 1111        |

| 6    | 110     | 001     | 0000        | 1111        |

| 7    | 111     | 000     | 0000        | 1111        |

# 2.同期回路プリミティブ

表 A2 ピンアサイン 表 A3 実験条件

| 信号名   | ピン番号 |

|-------|------|

| clock | 83   |

| d     | 49   |

| e     | 51   |

| nq    | 61   |

| q     | 57   |

| r     | 45   |

| e     | 52   |

|       |      |

|      | ンへら入りい |       |        |        |

|------|--------|-------|--------|--------|

| SW入力 | 2 進数値  | 反転信号値 | 出力信号値  | LED 点滅 |

| L    | r,e,d  | r,e,d | nq,q,x | nq,q,x |

| 0    | 000    | 111   | 011    | 100    |

| 1    | 001    | 110   | 100    | 011    |

| 2    | 010    | 101   | 100    | 011    |

| 3    | 011    | 100   | 100    | 011    |

| 4    | 100    | 011   | 101    | 010    |

| 5    | 101    | 010   | 100    | 011    |

| 6    | 110    | 001   | 100    | 011    |

| 7    | 111    | 000   | 100    | 011    |

# 3.周波数シンセサイザ

| 信号名 | ピン番号 |

|-----|------|

| clk | 83   |

| со  | 57   |

| hi0 | 40   |

| hi1 | 41   |

| hi2 | 39   |

| hi3 | 37   |

|     |      |

| lo0 | 49   |

| lo1 | 51   |

| 信号名 | ピン番号 |

|-----|------|

| lo2 | 45   |

| lo3 | 44   |

| on0 | 61   |

| on1 | 63   |

| on2 | 65   |

| on3 | 67   |

| on4 | 69   |

| on5 | 73   |

| q6  | 52   |